## INTEGRATED CIRCUITS

Product specification

2002 May 28

## SAA4979H

#### CONTENTS

| 1      | FEATURES                                    |

|--------|---------------------------------------------|

| 2      | GENERAL DESCRIPTION                         |

| 3      | QUICK REFERENCE DATA                        |

| 4      | ORDERING INFORMATION                        |

| 5      | BLOCK DIAGRAM                               |

| 6      | PINNING                                     |

| 7      | FUNCTIONAL DESCRIPTION                      |

| 7.1    | Digital processing at 1f <sub>H</sub> level |

| 7.1.1  | ITU 656 decoder                             |

| 7.1.2  | Double window and picture-in-picture        |

|        | processing                                  |

| 7.1.3  | Black bar detector                          |

| 7.1.4  | Dynamic noise reduction                     |

| 7.1.5  | Noise estimator                             |

| 7.2    | Embedded DRAM                               |

| 7.2.1  | 3.5-Mbit field memory                       |

| 7.3    | Digital processing at 2f <sub>H</sub> level |

| 7.3.1  | Sample rate conversion                      |

| 7.3.2  |                                             |

|        | Expansion port<br>Panoramic zoom            |

| 7.3.3  |                                             |

| 7.3.4  | Digital colour transient improvement        |

| 7.3.5  | Y horizontal smart peaking                  |

| 7.3.6  | Non-linear phase filter                     |

| 7.3.7  | Post processing                             |

| 7.4    | Triple 10-bit digital-to-analog conversion  |

| 7.5    | Microcontroller                             |

| 7.5.1  | Host interface                              |

| 7.5.2  | I <sup>2</sup> C-bus interface              |

| 7.5.3  | SNERT-bus                                   |

| 7.5.4  | I/O ports                                   |

| 7.5.5  | Watchdog timer                              |

| 7.5.6  | Reset                                       |

| 7.6    | System controller                           |

| 7.6.1  | Read enable output                          |

| 7.6.2  | Read enable input                           |

| 7.6.3  | Input enable                                |

| 7.6.4  | Horizontal deflection                       |

| 7.6.5  | Vertical deflection                         |

| 7.6.6  | Auxiliary display signal                    |

| 7.6.7  | Read enable 2                               |

| 7.6.8  | Output input enable 2                       |

| 7.6.9  | Reset read 2                                |

| 7.6.10 | Reset write 2                               |

| 7.7    | Line-locked clock generation                |

| 7.8    | Boundary scan test                          |

| 8    | CONTROL REGISTER DESCRIPTION                                                   |

|------|--------------------------------------------------------------------------------|

| 8.1  | Host interface detail                                                          |

| 8.2  | Special Function Registers (SFRs)                                              |

| 9    | LIMITING VALUES                                                                |

| 10   | THERMAL CHARACTERISTICS                                                        |

| 11   | CHARACTERISTICS                                                                |

| 12   | TRANSFER FUNCTIONS                                                             |

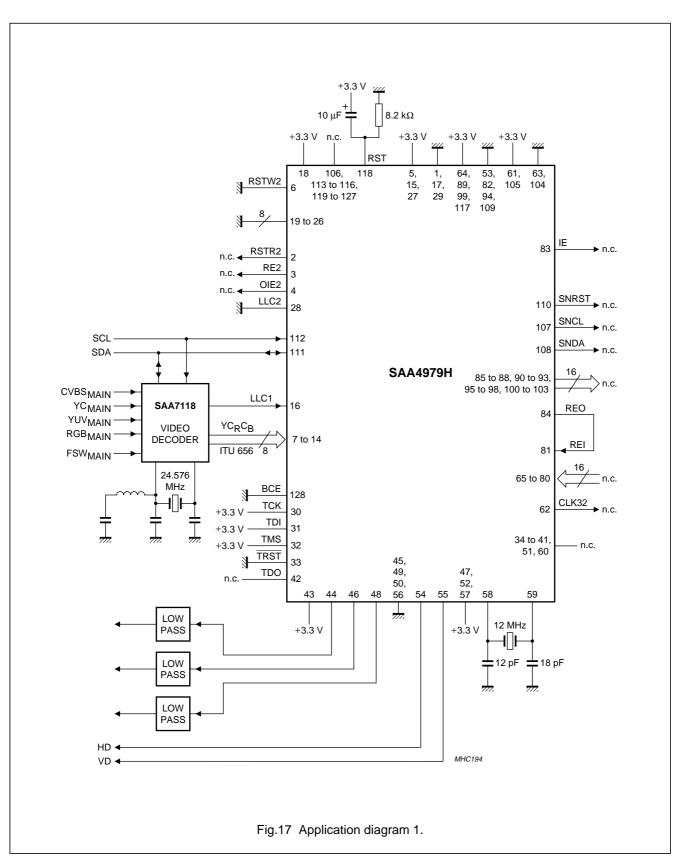

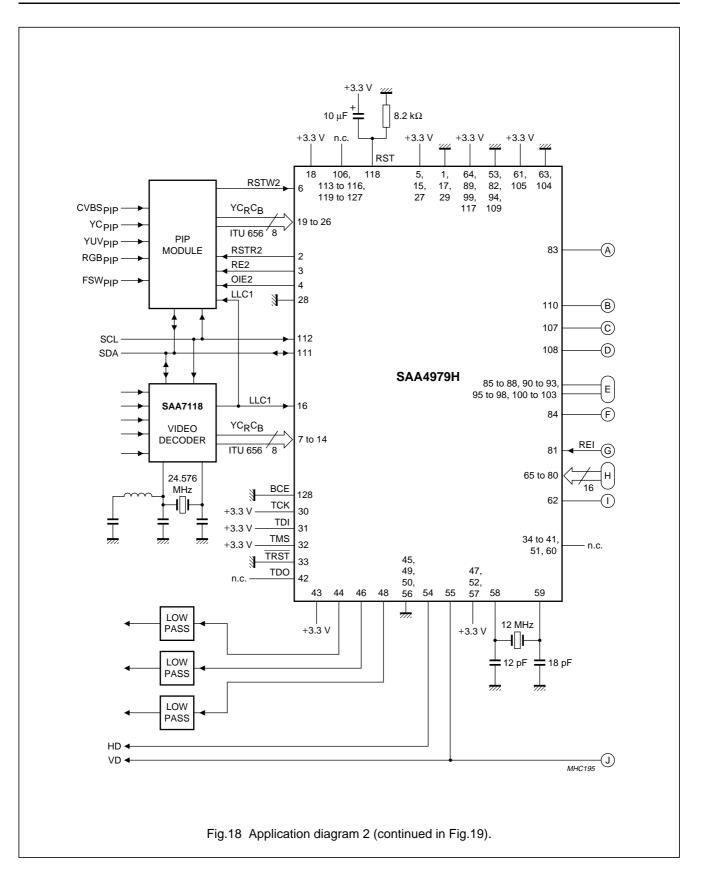

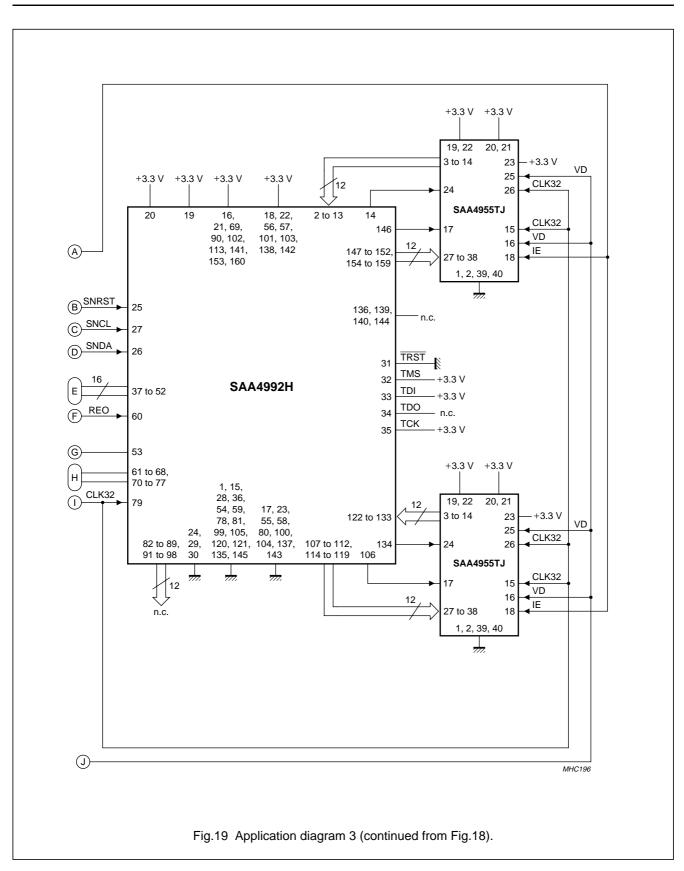

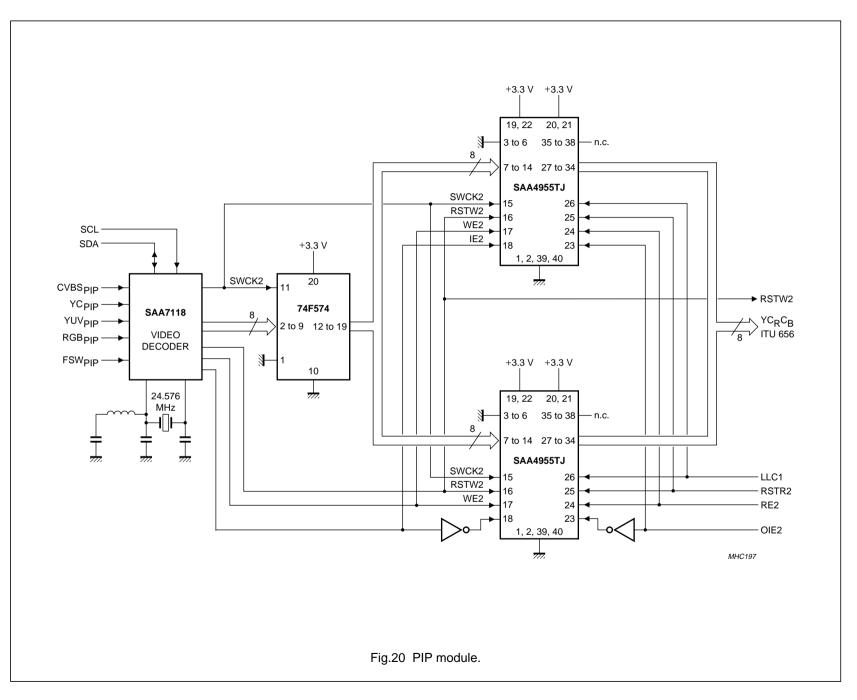

| 13   | APPLICATION INFORMATION                                                        |

| 14   | PACKAGE OUTLINE                                                                |

| 15   | SOLDERING                                                                      |

| 15.1 | Introduction to soldering surface mount<br>packages                            |

| 15.2 | Reflow soldering                                                               |

| 15.3 | Wave soldering                                                                 |

| 15.4 | Manual soldering                                                               |

| 15.5 | Suitability of surface mount IC packages for wave and reflow soldering methods |

| 16   | DATA SHEET STATUS                                                              |

| 17   | DEFINITIONS                                                                    |

| 18   | DISCLAIMERS                                                                    |

| 19   | PURCHASE OF PHILIPS I <sup>2</sup> C COMPONENTS                                |

|      |                                                                                |

|      |                                                                                |

### SAA4979H

#### 1 FEATURES

- Digital YUV input according to ITU 656 standard

- 4 : 2 : 2 field rate upconversion (50 to 100 Hz or 60 to 120 Hz)

- 3.5-Mbit embedded DRAM

- Sample rate conversion for linear zoom and compression

- Panorama mode

- Dynamic noise reduction

- Noise estimator

- Black bar detection

- Luminance horizontal smart peaking

- Digital Colour Transient Improvement (DCTI)

- Triple 10-bit Digital-to-Analog Converter (DAC)

- Line-locked PLL

- Expansion port for SAA4992H and SAA4991WP

- Double window and Picture-In-Picture (PIP) processing

- Embedded 80C51 microcontroller

- 32-Kbyte internal ROM (mask programmable)

- 512-byte internal RAM

#### **3 QUICK REFERENCE DATA**

- I<sup>2</sup>C-bus controlled

- Synchronous No parity Eight bit Reception and Transmission (SNERT) interface

- Boundary Scan Test (BST).

#### 2 GENERAL DESCRIPTION

The SAA4979H provides an economic stand-alone solution for 4 : 2 : 2 field rate upconversion (50 to 100 Hz or 60 to 120 Hz) including the required field memory combined with picture improvement features and dynamic field based noise reduction. The IC contains two digital input channels to allow field or frame based picture-in-picture processing. It also offers a feature expansion port for vector based motion estimation and compensation ICs such as SAA4991WP or SAA4992H.

| SYMBOL                              | PARAMETER                 | MIN. | TYP. | MAX. | UNIT |

|-------------------------------------|---------------------------|------|------|------|------|

| V <sub>DDD</sub>                    | digital supply voltage    | 3.0  | 3.3  | 3.6  | V    |

| V <sub>DDA</sub>                    | analog supply voltage     | 3.15 | 3.30 | 3.45 | V    |

| V <sub>DDO</sub> ; V <sub>DDI</sub> | I/O supply voltage        | 3.0  | 3.3  | 3.6  | V    |

| V <sub>DDP</sub>                    | protection supply voltage | 3.0  | 5.0  | 5.5  | V    |

| I <sub>DDD</sub>                    | digital supply current    | -    | 120  | 160  | mA   |

| I <sub>DDA</sub>                    | analog supply current     | _    | 40   | 50   | mA   |

| P <sub>tot</sub>                    | total power dissipation   | -    | -    | 0.9  | W    |

| T <sub>amb</sub>                    | ambient temperature       | -20  | _    | +70  | °C   |

#### 4 ORDERING INFORMATION

| TYPE     |        | PACKAGE                                                                                                             |          |  |  |  |  |  |  |

|----------|--------|---------------------------------------------------------------------------------------------------------------------|----------|--|--|--|--|--|--|

| NUMBER   | NAME   | DESCRIPTION                                                                                                         | VERSION  |  |  |  |  |  |  |

| SAA4979H | QFP128 | plastic quad flat package; 128 leads (lead length 1.6 mm); body $28 \times 28 \times 3.4$ mm; high stand-off height | SOT320-2 |  |  |  |  |  |  |

### SAA4979H

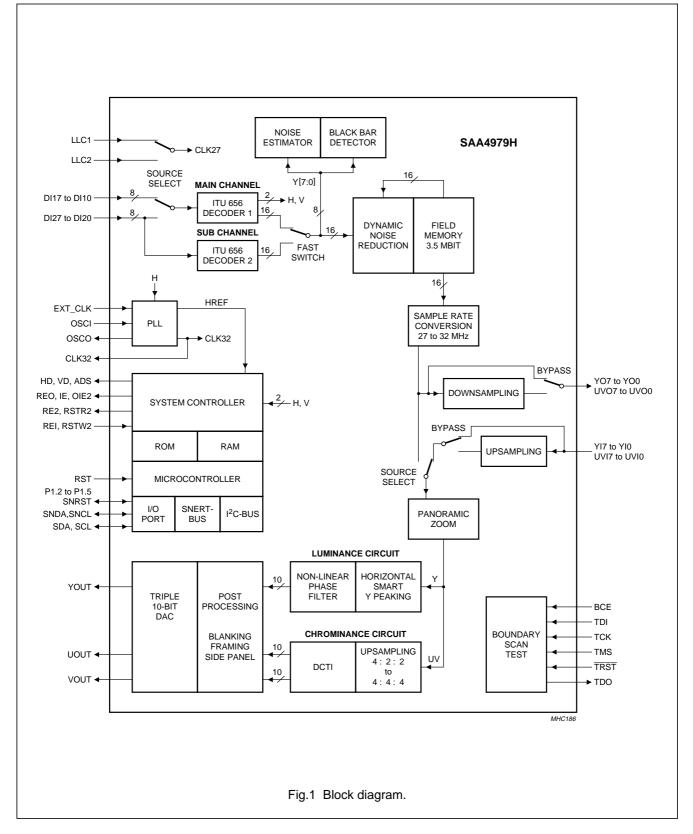

#### 5 BLOCK DIAGRAM

## SAA4979H

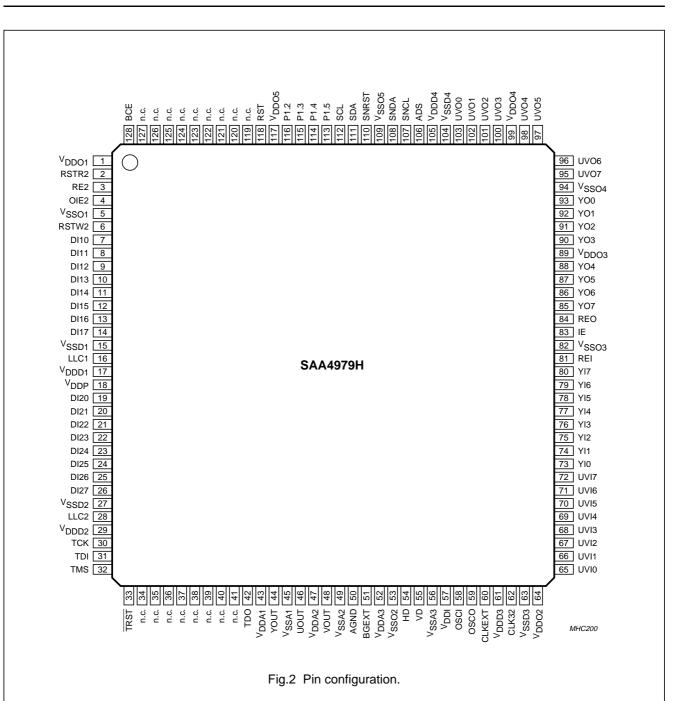

#### 6 PINNING

| SYMBOL            |          |                             | DESCRIPTION                         |

|-------------------|----------|-----------------------------|-------------------------------------|

| V <sub>DDO1</sub> | 1        | supply                      | I/O supply voltage 1 (3.3 V)        |

| RSTR2             | 2        | digital output (test input) | reset read, source 2                |

| RE2               | 3        | digital output (test input) | read enable, source 2               |

| OIE2              | 4        | digital output (test input) | output/input enable, source 2       |

| V <sub>SSO1</sub> | 5        | ground                      | I/O ground 1                        |

| RSTW2             | 6        | digital input               | reset write, source 2               |

| DI10              | 7        | digital input               | ITU 656 input bit 0 (LSB), source 1 |

| DI11              | 8        | digital input               | ITU 656 input bit 1, source 1       |

| DI12              | 9        | digital input               | ITU 656 input bit 2, source 1       |

| DI13              | 10       | digital input               | ITU 656 input bit 3, source 1       |

| DI14              | 11       | digital input               | ITU 656 input bit 4, source 1       |

| DI15              | 12       | digital input               | ITU 656 input bit 5, source 1       |

| DI16              | 13       | digital input               | ITU 656 input bit 6, source 1       |

| DI17              | 14       | digital input               | ITU 656 input bit 7 (MSB), source 1 |

| V <sub>SSD1</sub> | 15       | ground                      | digital ground 1                    |

| LLC1              | 16       | digital input               | 27 MHz clock signal, source 1       |

| V <sub>DDD1</sub> | 17       | supply                      | digital supply voltage 1 (3.3 V)    |

| V <sub>DDP</sub>  | 18       | supply                      | protection supply voltage (5 V)     |

| DI20              | 19       | digital input               | ITU 656 input bit 0 (LSB), source 2 |

| DI21              | 20       | digital input               | ITU 656 input bit 1, source 2       |

| DI22              | 21       | digital input               | ITU 656 input bit 2, source 2       |

| DI23              | 22       | digital input               | ITU 656 input bit 3, source 2       |

| DI24              | 23       | digital input               | ITU 656 input bit 4, source 2       |

| DI25              | 24       | digital input               | ITU 656 input bit 5, source 2       |

| DI26              | 25       | digital input               | ITU 656 input bit 6, source 2       |

| DI27              | 26       | digital input               | ITU 656 input bit 7 (MSB), source 2 |

| V <sub>SSD2</sub> | 27       | ground                      | digital ground 2                    |

| LLC2              | 28       | digital input               | 27 MHz clock signal, source 2       |

| V <sub>DDD2</sub> | 29       | supply                      | digital supply voltage 2 (3.3 V)    |

| ТСК               | 30       | digital input               | test clock                          |

| TDI               | 31       | digital input               | test data input                     |

| TMS               | 32       | digital input               | test mode select                    |

| TRST              | 33       | digital input               | test reset (active LOW)             |

| n.c.              | 34 to 41 | _                           | not connected                       |

| TDO               | 42       | digital output              | test data output                    |

| V <sub>DDA1</sub> | 43       | supply                      | analog supply voltage 1 (3.3 V)     |

| YOUT              | 44       | analog output               | Y analog output                     |

| V <sub>SSA1</sub> | 45       | ground                      | analog ground 1                     |

| UOUT              | 46       | analog output               | –(B – Y) analog output              |

| V <sub>DDA2</sub> | 47       | supply                      | analog supply voltage 2 (3.3 V)     |

| SYMBOL            | PIN | TYPE           | DESCRIPTION                                     |

|-------------------|-----|----------------|-------------------------------------------------|

| VOUT              | 48  | analog output  | –(R – Y) analog output                          |

| V <sub>SSA2</sub> | 49  | ground         | analog ground 2                                 |

| AGND              | 50  | ground         | analog ground (without substrate contacts)      |

| BGEXT             | 51  | analog I/O     | band gap external I/O                           |

| V <sub>DDA3</sub> | 52  | supply         | analog supply voltage 3 (3.3 V)                 |

| V <sub>SSO2</sub> | 53  | ground         | I/O ground 2                                    |

| HD                | 54  | digital output | horizontal synchronisation output, display part |

| VD                | 55  | digital output | vertical synchronisation output, display part   |

| V <sub>SSA3</sub> | 56  | ground         | analog ground 3                                 |

| V <sub>DDI</sub>  | 57  | supply         | I/O internal supply voltage (3.3 V)             |

| OSCI              | 58  | analog input   | oscillator input                                |

| OSCO              | 59  | analog output  | oscillator output                               |

| CLKEXT            | 60  | digital input  | external clock input                            |

| V <sub>DDD3</sub> | 61  | supply         | digital supply voltage 3 (3.3 V)                |

| CLK32             | 62  | digital output | 32 MHz clock output                             |

| V <sub>SSD3</sub> | 63  | ground         | digital ground 3                                |

| V <sub>DDO2</sub> | 64  | supply         | I/O supply voltage 2 (3.3 V)                    |

| UVI0              | 65  | digital input  | UV digital input bit 0 (LSB)                    |

| UVI1              | 66  | digital input  | UV digital input bit 1                          |

| UVI2              | 67  | digital input  | UV digital input bit 2                          |

| UVI3              | 68  | digital input  | UV digital input bit 3                          |

| UVI4              | 69  | digital input  | UV digital input bit 4                          |

| UVI5              | 70  | digital input  | UV digital input bit 5                          |

| UVI6              | 71  | digital input  | UV digital input bit 6                          |

| UVI7              | 72  | digital input  | UV digital input bit 7 (MSB)                    |

| YIO               | 73  | digital input  | Y digital input bit 0 (LSB)                     |

| YI1               | 74  | digital input  | Y digital input bit 1                           |

| YI2               | 75  | digital input  | Y digital input bit 2                           |

| YI3               | 76  | digital input  | Y digital input bit 3                           |

| YI4               | 77  | digital input  | Y digital input bit 4                           |

| YI5               | 78  | digital input  | Y digital input bit 5                           |

| YI6               | 79  | digital input  | Y digital input bit 6                           |

| YI7               | 80  | digital input  | Y digital input bit 7 (MSB)                     |

| REI               | 81  | digital input  | read enable input                               |

| V <sub>SSO3</sub> | 82  | ground         | I/O ground 3                                    |

| IE                | 83  | digital output | input enable                                    |

| REO               | 84  | digital output | read enable output                              |

| YO7               | 85  | digital output | Y digital output bit 7 (MSB)                    |

| YO6               | 86  | digital output | Y digital output bit 6                          |

| YO5               | 87  | digital output | Y digital output bit 5                          |

| YO4               | 88  | digital output | Y digital output bit 4                          |

| VDDD389supplyI/O supply voltage 3 (3.3 V)YQ390digital outputY digital output bit 3YQ291digital outputY digital output bit 2YO192digital outputY digital output bit 1YO093digital outputY digital output bit 0 (LSB)VSS0494groundI/O ground 4UVO795digital outputU/ digital output bit 7 (MSB)UVO696digital outputU/ digital output bit 5UVO498digital outputU/ digital output bit 5UVO498digital outputU/ digital output bit 3UVO498digital outputU/ digital output bit 3UVO2101digital outputU/ digital output bit 3UVO2101digital outputU/ digital output bit 1UVO2101digital outputU/ digital output bit 1UVO2101digital outputU/ digital output bit 1UVO2101digital outputU/ digital output bit 1UVO1102digital outputU/ digital output bit 1UVO2101digital outputU/ digital output bit 0 (LSB)Vspp4104grounddigital ground 4VDD4105supplydigital supply voltage 4 (3.3 V)ADS106digital outputSNERT clockSNDA108digital ivputSNERT clockSNDA108digital ivputSNERT clockSNRST110digital I/OSNERT cloc                                                                                                                                                                         | SYMBOL            | PIN        | ТҮРЕ           | DESCRIPTION                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------|----------------|---------------------------------------------|

| YO291digital outputY digital output bit 2YO192digital outputY digital output bit 1YO093digital outputY digital output bit 0 (LSB)Vsso494groundI/O ground 4UV0795digital outputUV digital output bit 7 (MSB)UV0696digital outputUV digital output bit 6UV0597digital outputUV digital output bit 5UV0498digital outputUV digital output bit 4VpD0499supplyI/O supply voltage 4 (3.3 V)UV03100digital outputUV digital output bit 3UV02101digital outputUV digital output bit 2UV01102digital outputUV digital output bit 0 (LSB)VspD4103digital outputUV digital output bit 0 (LSB)VV02101digital outputUV digital output bit 0 (LSB)VSpD4105supplydigital supply voltage 4 (3.3 V)UV01102digital outputUV digital output bit 0 (LSB)VspD4105supplydigital supply voltage 4 (3.3 V)ADS106digital outputSNERT clockSNDA108digital //OSNERT clockSNDA108digital //OSNERT restart (port 1.0)SDA111digital I/OFC-bus scick (port 1.6)P1.5113digital I/Oport 1 data input/output signal 5P1.4114digital I/Oport 1 data input/output signal 4<                                                                                                                                          | V <sub>DDO3</sub> | 89         | supply         | I/O supply voltage 3 (3.3 V)                |

| YO192digital outputY digital output bit 1YO093digital outputY digital output bit 0 (LSB)Ysso494groundI/O ground 4UVO795digital outputUV digital output bit 7 (MSB)UVO696digital outputUV digital output bit 6UVO597digital outputUV digital output bit 5UVO498digital outputUV digital output bit 5UVO498digital outputUV digital output bit 3UVO3100digital outputUV digital output bit 3UVO2101digital outputUV digital output bit 2UVO1102digital outputUV digital output bit 1UVO2101digital outputUV digital output bit 0 (LSB)VsD499supplyUV digital output bit 2UVO1102digital outputUV digital output bit 0 (LSB)VsD4105supplydigital ground 4UVO0103digital outputut digital ground 4VD04105supplydigital ground 4VD04106digital outputut digital ground 4VD05106digital outputauxiliary display signalSNCL107digital outputSNERT clockSNDA108digital //OSNERT restart (port 1.0)SNRST110digital //OI²C-bus clock (port 1.6)P1.5113digital //Oport 1 data input/output signal 5P1.4114digital //O <t< td=""><td></td><td>90</td><td>digital output</td><td>Y digital output bit 3</td></t<>                                                                             |                   | 90         | digital output | Y digital output bit 3                      |

| YO093digital outputY digital output bit 0 (LSB)Vsso494groundI/O ground 4UVO795digital outputUV digital output bit 7 (MSB)UVO696digital outputUV digital output bit 6UVO597digital outputUV digital output bit 5UVO498digital outputUV digital output bit 5UVO3100digital outputUV digital output bit 3UVO2101digital outputUV digital output bit 3UVO2101digital outputUV digital output bit 1UVO2101digital outputUV digital output bit 1UVO1102digital outputUV digital output bit 0 (LSB)Vssp4104grounddigital ground 4Vbop495supplydigital ground 4VV00103digital outputUV digital output bit 0 (LSB)Vssp4104grounddigital ground 4Vbop4105supplydigital ground 4Vbop4105supplydigital ground 4Vssp4106digital outputSNERT serial 4(3.3 V)ADS106digital outputSNERT serial dataNSc107digital outputSNERT serial dataVsso5109groundmicrocontroller I/O groundSNRST110digital I/OSNERT restart (port 1.6)P1.5113digital I/Oport 1 data input/output signal 5P1.4114digital I/Oport 1 data input/output                                                                                                                                                                         | YO2               | 91         | digital output | Y digital output bit 2                      |

| Vsso494groundI/O ground 4UVO795digital outputUV digital output bit 7 (MSB)UVO696digital outputUV digital output bit 6UVO597digital outputUV digital output bit 5UVO498digital outputUV digital output bit 3UVO3100digital outputUV digital output bit 3UVO2101digital outputUV digital output bit 2UVO3100digital outputUV digital output bit 1UVO2101digital outputUV digital output bit 1UVO1102digital outputUV digital output bit 0 (LSB)VssD4104grounddigital ground 4VD004105supplydigital ground 4VSD4105supplydigital ground 4VSD4106digital outputUV digital output bit 0 (LSB)VssD4106digital outputauxiliary display signalSNCL107digital outputSNERT clockSNDA108digital I/OSNERT serial dataVsso5109groundmicrocontroller I/O groundSNRST110digital I/OIPC-bus serial data (port 1.7)SCL112digital I/OIPC-bus clock (port 1.6)P1.5113digital I/Oport 1 data input/output signal 5P1.4114digital I/Oport 1 data input/output signal 3P1.2116digital I/Oport 1 data input/output signal 3P1.2116digita                                                                                                                                                                | YO1               | 92         | digital output | Y digital output bit 1                      |

| UV0795digital outputUV digital output bit 7 (MSB)UV0696digital outputUV digital output bit 6UV0597digital outputUV digital output bit 5UV0498digital outputUV digital output bit 4V <sub>D04</sub> 99supplyI/O supply voltage 4 (3.3 V)UV03100digital outputUV digital output bit 3UV02101digital outputUV digital output bit 3UV01102digital outputUV digital output bit 1UV00103digital outputUV digital output bit 1UV01102digital outputUV digital output bit 0 (LSB)VSD4104grounddigital ground 4VopD4105supplydigital supply voltage 4 (3.3 V)ADS106digital outputSNERT clockSNL107digital outputSNERT clockSNDA108digital I/OSNERT serial dataV <sub>SS05</sub> 109groundmicrocontroller I/O groundSNRST110digital I/OI²C-bus serial data (port 1.7)SCL112digital I/OI²C-bus clock (port 1.6)P1.5113digital I/Oport 1 data input/output signal 5P1.4114digital I/Oport 1 data input/output signal 4P1.2116digital I/Oport 1 data input/output signal 2V <sub>D005</sub> 117supplymicrocontroller I/O supply voltage (3.3 V)RST118digital I/Oport 1 data input/output signal 2 </td <td>YO0</td> <td>93</td> <td>digital output</td> <td>Y digital output bit 0 (LSB)</td> | YO0               | 93         | digital output | Y digital output bit 0 (LSB)                |

| UVO795digital outputUV digital output bit 7 (MSB)UVO696digital outputUV digital output bit 6UVO597digital outputUV digital output bit 5UVO498digital outputUV digital output bit 4Vpoo499supplyI/O supply voltage 4 (3.3 V)UVO3100digital outputUV digital output bit 3UVO2101digital outputUV digital output bit 2UVO1102digital outputUV digital output bit 1UVO0103digital outputUV digital output bit 1UVO0103digital outputUV digital output bit 1UVO0103digital outputUV digital output bit 0 (LSB)VSD4104grounddigital ground 4VDD4105supplydigital supply voltage 4 (3.3 V)ADS106digital outputSNERT clockSNCL107digital outputSNERT clockSNDA108digital I/OSNERT serial dataV <sub>SSO5</sub> 109groundmicrocontroller I/O groundSNRST110digital I/OI²C-bus serial data (port 1.7)SCL112digital I/Oport 1 data input/output signal 5P1.5113digital I/Oport 1 data input/output signal 4P1.2116digital I/Oport 1 data input/output signal 3P1.4114digital I/Oport 1 data input/output signal 3P1.4114digital I/Oport 1 data input/output signal 3 </td <td>V<sub>SSO4</sub></td> <td>94</td> <td>ground</td> <td>I/O ground 4</td>                                       | V <sub>SSO4</sub> | 94         | ground         | I/O ground 4                                |

| UVOS97digital outputUV digital output bit 5UVO498digital outputUV digital output bit 4V <sub>DD04</sub> 99supplyI/O supply voltage 4 (3.3 V)UVO3100digital outputUV digital output bit 3UVO2101digital outputUV digital output bit 2UVO1102digital outputUV digital output bit 1UVO0103digital outputUV digital output bit 0 (LSB)VSD4104grounddigital ground 4VDD4105supplydigital supply voltage 4 (3.3 V)ADS106digital outputauxiliary display signalSNCL107digital outputSNERT clockSNDA108digital I/OSNERT restart (port 1.0)SNRST110digital I/OI²C-bus serial data (port 1.7)SCL112digital I/OI²C-bus serial data (port 1.7)SCL113digital I/Oport 1 data input/output signal 5P1.4114digital I/Oport 1 data input/output signal 4P1.3115digital I/Oport 1 data input/output signal 3P1.2116digital I/Oport 1 data input/output signal 3P1.2116digital I/Oport 1 data input/output signal 2V <sub>DDO5</sub> 117supplymicrocontroller I/O supply voltage (3.3 V)RST118digital inputmicrocontroller reset inputn.c.119 to 127-not connected                                                                                                                                  |                   | 95         | digital output | UV digital output bit 7 (MSB)               |

| UV0498digital outputUV digital output bit 4 $V_{DD04}$ 99supplyI/O supply voltage 4 (3.3 V)UV03100digital outputUV digital output bit 3UV02101digital outputUV digital output bit 2UV01102digital outputUV digital output bit 1UV00103digital outputUV digital output bit 0 (LSB)VSD4104grounddigital ground 4VDD4105supplydigital supply voltage 4 (3.3 V)ADS106digital outputSNERT clockSNCL107digital outputSNERT clockSNDA108digital I/OSNERT serial dataVso5109groundmicrocontroller I/O groundSNRST110digital I/OI <sup>2</sup> C-bus serial data (port 1.7)SCL112digital I/OI <sup>2</sup> C-bus clock (port 1.6)P1.5113digital I/Oport 1 data input/output signal 5P1.4114digital I/Oport 1 data input/output signal 3P1.2116digital I/Oport 1 data input/output signal 3P1.2116digital I/Oport 1 data input/output signal 3P1.2118digital I/Oport 1 data input/output signal 3P1.2118digital inputmicrocontroller I/O supply voltage (3.3 V)                                                                                                                                                                                                                            | UVO6              | 96         | digital output | UV digital output bit 6                     |

| V<br>DD0499SupplyI/O Supply voltage 4 (3.3 V)UV03100digital outputUV digital output bit 3UV02101digital outputUV digital output bit 2UV01102digital outputUV digital output bit 1UV00103digital outputUV digital output bit 0 (LSB)Vs5b4104grounddigital supply voltage 4 (3.3 V)ADS106digital outputuxiliary display signalSNCL107digital outputSNERT clockSNDA108digital I/OSNERT serial dataVs505109groundmicrocontroller I/O groundSNRST110digital I/OSNERT restart (port 1.0)SDA111digital I/OI²C-bus serial data (port 1.7)SCL112digital I/Oport 1 data input/output signal 5P1.4114digital I/Oport 1 data input/output signal 4P1.3115digital I/Oport 1 data input/output signal 3P1.2116digital I/Oport 1 data input/output signal 2Vb005117supplymicrocontroller I/O supply voltage (3.3 V)RST118digital I/Oport 1 data input/output signal 2                                                                                                                                                                                                                                                                                                                           | UVO5              | 97         | digital output | UV digital output bit 5                     |

| UV03100digital outputUV digital output bit 3UV02101digital outputUV digital output bit 3UV01102digital outputUV digital output bit 1UV00103digital outputUV digital output bit 0 (LSB)VsD4104grounddigital supply voltage 4 (3.3 V)ADS106digital outputsNERT clockSNCL107digital outputSNERT clockSNDA108digital I/OSNERT serial dataVsS05109groundmicrocontroller I/O groundSNRST110digital I/OSNERT restart (port 1.0)SDA111digital I/OI²C-bus serial data (port 1.7)SCL112digital I/OI²C-bus clock (port 1.6)P1.5113digital I/Oport 1 data input/output signal 5P1.4114digital I/Oport 1 data input/output signal 3P1.2116digital I/Oport 1 data input/output signal 2VDD5117supplymicrocontroller I/O supply voltage (3.3 V)RST118digital inputmicrocontroller I/O supply voltage (3.3 V)RST118digital inputmicrocontroller reset inputn.c.119 to 127-not connected                                                                                                                                                                                                                                                                                                          | UVO4              | 98         | digital output | UV digital output bit 4                     |

| UVO2101digital outputUV digital output bit 2UV01102digital outputUV digital output bit 1UV00103digital outputUV digital output bit 0 (LSB)VSD4104grounddigital ground 4VDD4105supplydigital supply voltage 4 (3.3 V)ADS106digital outputauxiliary display signalSNCL107digital outputSNERT clockSNDA108digital //OSNERT serial dataV <sub>SSO5</sub> 109groundmicrocontroller I/O groundSNRST110digital I/OSNERT restart (port 1.0)SDA111digital I/OI²C-bus serial data (port 1.7)SCL112digital I/OI²C-bus clock (port 1.6)P1.5113digital I/Oport 1 data input/output signal 5P1.4114digital I/Oport 1 data input/output signal 3P1.2116digital I/Oport 1 data input/output signal 3P1.2118digital I/Oport 1 data input/output signal 2VDD5117supplymicrocontroller I/O supply voltage (3.3 V)RST118digital inputmicrocontroller reset inputn.c.119 to 127-not connected                                                                                                                                                                                                                                                                                                         | V <sub>DDO4</sub> | 99         | supply         | I/O supply voltage 4 (3.3 V)                |

| UVO1102digital outputUV digital output bit 1UVO0103digital outputUV digital output bit 0 (LSB)VSSD4104grounddigital ground 4VDD04105supplydigital supply voltage 4 (3.3 V)ADS106digital outputauxiliary display signalSNCL107digital outputSNERT clockSNDA108digital I/OSNERT serial dataV <sub>SSO5</sub> 109groundmicrocontroller I/O groundSNRST110digital I/OSNERT restart (port 1.0)SDA111digital I/OI²C-bus serial data (port 1.7)SCL112digital I/OI²C-bus clock (port 1.6)P1.5113digital I/Oport 1 data input/output signal 5P1.4114digital I/Oport 1 data input/output signal 4P1.3115digital I/Oport 1 data input/output signal 3P1.2116digital I/Oport 1 data input/output signal 2VDD05117supplymicrocontroller I/O supply voltage (3.3 V)RST118digital inputmicrocontroller I/O supply voltage (3.3 V)RST118digital inputmicrocontroller I/O supply voltage (3.3 V)                                                                                                                                                                                                                                                                                                  | UVO3              | 100        | digital output | UV digital output bit 3                     |

| UV00103digital outputUV digital output bit 0 (LSB)V_SSD4104grounddigital ground 4VDDD4105supplydigital supply voltage 4 (3.3 V)ADS106digital outputauxiliary display signalSNCL107digital outputSNERT clockSNDA108digital I/OSNERT serial dataV_SS05109groundmicrocontroller I/O groundSNRST110digital I/OSNERT restart (port 1.0)SDA111digital I/OI²C-bus serial data (port 1.7)SCL112digital I/OI²C-bus clock (port 1.6)P1.5113digital I/Oport 1 data input/output signal 5P1.4114digital I/Oport 1 data input/output signal 3P1.2116digital I/Oport 1 data input/output signal 3P1.2118digital I/Oport 1 data input/output signal 2VDDO5117supplymicrocontroller I/O supply voltage (3.3 V)RST118digital inputmicrocontroller reset inputn.c.119 to 127-not connected                                                                                                                                                                                                                                                                                                                                                                                                         | UVO2              | 101        | digital output | UV digital output bit 2                     |

| VSSD4104grounddigital ground 4VDDD4105supplydigital supply voltage 4 (3.3 V)ADS106digital outputauxiliary display signalSNCL107digital outputSNERT clockSNDA108digital I/OSNERT serial dataVSSO5109groundmicrocontroller I/O groundSNRST110digital I/OSNERT restart (port 1.0)SDA111digital I/OI²C-bus serial data (port 1.7)SCL112digital I/OI²C-bus clock (port 1.6)P1.5113digital I/Oport 1 data input/output signal 5P1.4114digital I/Oport 1 data input/output signal 4P1.3115digital I/Oport 1 data input/output signal 3P1.2116digital I/Oport 1 data input/output signal 3P1.2118digital I/Oport 1 data input/output signal 2NDD5117supplymicrocontroller I/O supply voltage (3.3 V)RST118digital inputmicrocontroller reset inputn.c.119 to 127-not connected                                                                                                                                                                                                                                                                                                                                                                                                           | UVO1              | 102        | digital output | UV digital output bit 1                     |

| VDDD4105supplydigital supply voltage 4 (3.3 V)ADS106digital outputauxiliary display signalSNCL107digital outputSNERT clockSNDA108digital I/OSNERT serial dataVSSO5109groundmicrocontroller I/O groundSNRST110digital I/OSNERT restart (port 1.0)SDA111digital I/OI²C-bus serial data (port 1.7)SCL112digital I/OI²C-bus clock (port 1.6)P1.5113digital I/Oport 1 data input/output signal 5P1.4114digital I/Oport 1 data input/output signal 4P1.3115digital I/Oport 1 data input/output signal 3P1.2116digital I/Oport 1 data input/output signal 2VDD05117supplymicrocontroller I/O supply voltage (3.3 V)RST118digital inputmicrocontroller reset inputn.c.119 to 127-not connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | UVO0              | 103        | digital output | UV digital output bit 0 (LSB)               |

| VDDD4105supplydigital supply voltage 4 (3.3 V)ADS106digital outputauxiliary display signalSNCL107digital outputSNERT clockSNDA108digital I/OSNERT serial dataVSSO5109groundmicrocontroller I/O groundSNRST110digital I/OSNERT restart (port 1.0)SDA111digital I/OI²C-bus serial data (port 1.7)SCL112digital I/OI²C-bus clock (port 1.6)P1.5113digital I/Oport 1 data input/output signal 5P1.4114digital I/Oport 1 data input/output signal 4P1.3115digital I/Oport 1 data input/output signal 3P1.2116digital I/Oport 1 data input/output signal 2VDD05117supplymicrocontroller I/O supply voltage (3.3 V)RST118digital inputmicrocontroller reset inputn.c.119 to 127-not connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V <sub>SSD4</sub> | 104        | ground         | digital ground 4                            |

| SNCL107digital outputSNERT clockSNDA108digital I/OSNERT serial dataV <sub>SSO5</sub> 109groundmicrocontroller I/O groundSNRST110digital I/OSNERT restart (port 1.0)SDA111digital I/OI²C-bus serial data (port 1.7)SCL112digital I/OI²C-bus clock (port 1.6)P1.5113digital I/Oport 1 data input/output signal 5P1.4114digital I/Oport 1 data input/output signal 4P1.3115digital I/Oport 1 data input/output signal 3P1.2116digital I/Oport 1 data input/output signal 2V <sub>DDO5</sub> 117supplymicrocontroller I/O supply voltage (3.3 V)RST118digital inputmicrocontroller reset inputn.c.119 to 127-not connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                   | 105        | supply         | digital supply voltage 4 (3.3 V)            |

| SNDA108digital I/OSNERT serial dataV <sub>SSO5</sub> 109groundmicrocontroller I/O groundSNRST110digital I/OSNERT restart (port 1.0)SDA111digital I/OI²C-bus serial data (port 1.7)SCL112digital I/OI²C-bus clock (port 1.6)P1.5113digital I/Oport 1 data input/output signal 5P1.4114digital I/Oport 1 data input/output signal 4P1.3115digital I/Oport 1 data input/output signal 3P1.2116digital I/Oport 1 data input/output signal 2V <sub>DDO5</sub> 117supplymicrocontroller I/O supply voltage (3.3 V)RST118digital inputmicrocontroller reset inputn.c.119 to 127-not connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ADS               | 106        | digital output | auxiliary display signal                    |

| VSSO5109groundmicrocontroller I/O groundSNRST110digital I/OSNERT restart (port 1.0)SDA111digital I/OI²C-bus serial data (port 1.7)SCL112digital I/OI²C-bus clock (port 1.6)P1.5113digital I/Oport 1 data input/output signal 5P1.4114digital I/Oport 1 data input/output signal 4P1.3115digital I/Oport 1 data input/output signal 3P1.2116digital I/Oport 1 data input/output signal 2VDDO5117supplymicrocontroller I/O supply voltage (3.3 V)RST118digital inputmicrocontroller reset inputn.c.119 to 127-not connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SNCL              | 107        | digital output | SNERT clock                                 |

| SNRST110digital I/OSNERT restart (port 1.0)SDA111digital I/OI²C-bus serial data (port 1.7)SCL112digital I/OI²C-bus clock (port 1.6)P1.5113digital I/Oport 1 data input/output signal 5P1.4114digital I/Oport 1 data input/output signal 4P1.3115digital I/Oport 1 data input/output signal 3P1.2116digital I/Oport 1 data input/output signal 2VDD05117supplymicrocontroller I/O supply voltage (3.3 V)RST118digital inputmicrocontroller reset inputn.c.119 to 127-not connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SNDA              | 108        | digital I/O    | SNERT serial data                           |

| SDA111digital I/OI²C-bus serial data (port 1.7)SCL112digital I/OI²C-bus clock (port 1.6)P1.5113digital I/Oport 1 data input/output signal 5P1.4114digital I/Oport 1 data input/output signal 4P1.3115digital I/Oport 1 data input/output signal 3P1.2116digital I/Oport 1 data input/output signal 2VDD05117supplymicrocontroller I/O supply voltage (3.3 V)RST118digital inputmicrocontroller reset inputn.c.119 to 127-not connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V <sub>SSO5</sub> | 109        | ground         | microcontroller I/O ground                  |

| SCL112digital I/OI²C-bus clock (port 1.6)P1.5113digital I/Oport 1 data input/output signal 5P1.4114digital I/Oport 1 data input/output signal 4P1.3115digital I/Oport 1 data input/output signal 3P1.2116digital I/Oport 1 data input/output signal 2VDD05117supplymicrocontroller I/O supply voltage (3.3 V)RST118digital inputmicrocontroller reset inputn.c.119 to 127–not connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | SNRST             | 110        | digital I/O    | SNERT restart (port 1.0)                    |

| P1.5113digital I/Oport 1 data input/output signal 5P1.4114digital I/Oport 1 data input/output signal 4P1.3115digital I/Oport 1 data input/output signal 3P1.2116digital I/Oport 1 data input/output signal 2VDD05117supplymicrocontroller I/O supply voltage (3.3 V)RST118digital inputmicrocontroller reset inputn.c.119 to 127–not connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | SDA               | 111        | digital I/O    | I <sup>2</sup> C-bus serial data (port 1.7) |

| P1.4114digital I/Oport 1 data input/output signal 4P1.3115digital I/Oport 1 data input/output signal 3P1.2116digital I/Oport 1 data input/output signal 2VDD05117supplymicrocontroller I/O supply voltage (3.3 V)RST118digital inputmicrocontroller reset inputn.c.119 to 127-not connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | SCL               | 112        | digital I/O    | I <sup>2</sup> C-bus clock (port 1.6)       |

| P1.3115digital I/Oport 1 data input/output signal 3P1.2116digital I/Oport 1 data input/output signal 2VDD05117supplymicrocontroller I/O supply voltage (3.3 V)RST118digital inputmicrocontroller reset inputn.c.119 to 127–not connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | P1.5              | 113        | digital I/O    | port 1 data input/output signal 5           |

| P1.2116digital I/Oport 1 data input/output signal 2VDD05117supplymicrocontroller I/O supply voltage (3.3 V)RST118digital inputmicrocontroller reset inputn.c.119 to 127–not connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | P1.4              | 114        | digital I/O    | port 1 data input/output signal 4           |

| V <sub>DDO5</sub> 117         supply         microcontroller I/O supply voltage (3.3 V)           RST         118         digital input         microcontroller reset input           n.c.         119 to 127         –         not connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | P1.3              | 115        | digital I/O    | port 1 data input/output signal 3           |

| RST     118     digital input     microcontroller reset input       n.c.     119 to 127     –     not connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | P1.2              | 116        | digital I/O    | port 1 data input/output signal 2           |

| RST118digital inputmicrocontroller reset inputn.c.119 to 127-not connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | V <sub>DDO5</sub> | 117        | supply         | microcontroller I/O supply voltage (3.3 V)  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | RST               | 118        | digital input  | microcontroller reset input                 |

| BCE 128 digital input boundary scan compliant enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | n.c.              | 119 to 127 | -              | not connected                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | BCE               | 128        | digital input  | boundary scan compliant enable              |

SAA4979H

## Sample rate converter with embedded high quality dynamic noise reduction and expansion port

#### Product specification

## Sample rate converter with embedded high quality dynamic noise reduction and expansion port

### SAA4979H

#### 7 FUNCTIONAL DESCRIPTION

#### 7.1 Digital processing at 1f<sub>H</sub> level

#### 7.1.1 ITU 656 DECODER

The SAA4979H provides 2 digital video input channels, which comply to the ITU 656 standard.

720 active video pixels per line are processed at a line-locked clock of 27 MHz, which has to be provided by the signal source. Luminance and chrominance information have to be multiplexed in the following order:  $C_{B1}$ ,  $Y_1$ ,  $C_{R1}$ ,  $Y_2$ , ... Timing reference codes must be inserted at the beginning and end of each video line (see Table 1):

- A 'Start of Active Video' (SAV) code before the first active video sample (see Table 2)

- A 'End of Active Video' (EAV) code after the last active video sample (see Table 2).

The incoming active video data must be limited to 1 to 254, since the data words 00H and FFH are used for identification of the timing reference headers.

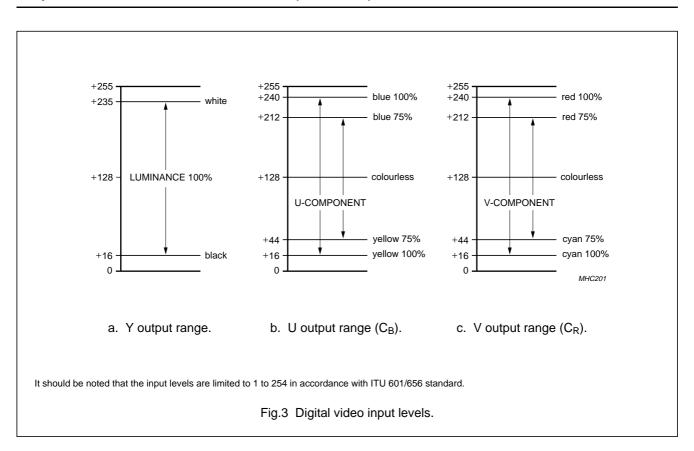

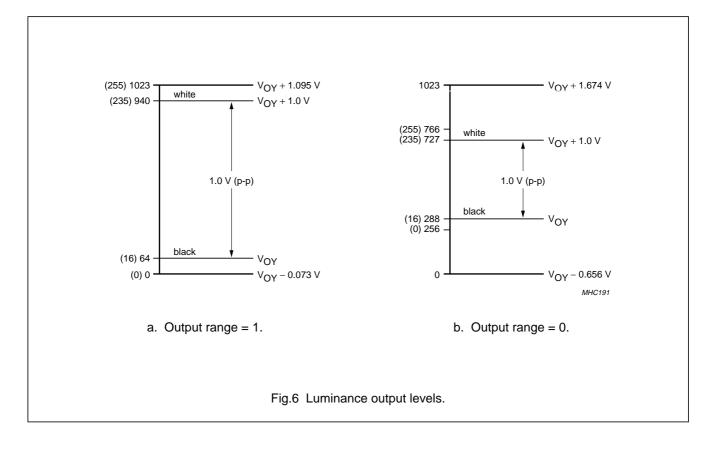

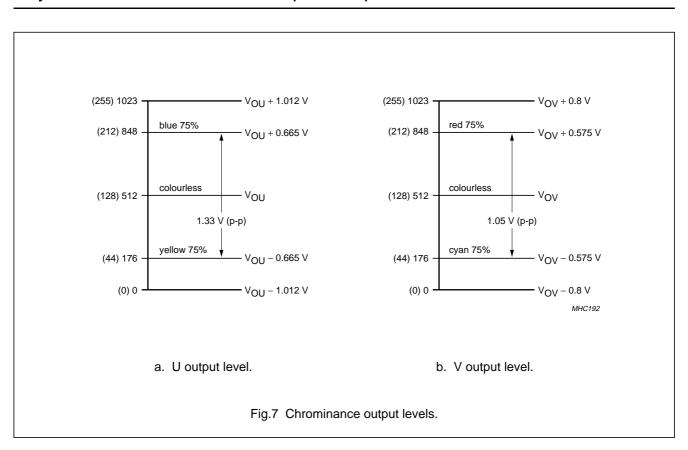

The digital signal input levels should comply to the CCIR-601 standard (see Fig.3). The data stream is decoded into the internal 4 : 2 : 2 YUV format at a 13.5 MHz clock rate. If required the sign of the UV signals can be inverted for both channels (control inputs: uv\_sign1 and uv\_sign2).

The signal source of the main channel can be selected from both inputs by the internal microcontroller (control input: Select\_data\_input1).

| Table 1         ITU data format |

|---------------------------------|

|                                 |

| ANKI   | -  |    | EFE | /ING<br>REN<br>E (HI | ICE |         | 7  | 20 PI)           | KELS | S YUV            | 4:2 | 2:2 | DATA               |      |    | EFE | /ING<br>REN<br>E (HI | ICE |    | ANKI<br>ERIO |  |

|--------|----|----|-----|----------------------|-----|---------|----|------------------|------|------------------|-----|-----|--------------------|------|----|-----|----------------------|-----|----|--------------|--|

| <br>80 | 10 | FF | 00  | 00                   | SAV | $C_B 0$ | Y0 | C <sub>R</sub> 0 | Y1   | C <sub>B</sub> 2 | Y2  |     | C <sub>R</sub> 718 | Y719 | FF | 00  | 00                   | EAV | 80 | 10           |  |

#### Table 2SAV/EAV format

| BIT 7 | BIT 6                                              | BIT 5                                                            | BIT 4                                       | BIT 3  | BIT 2 | BIT 1                            | BIT 0 |

|-------|----------------------------------------------------|------------------------------------------------------------------|---------------------------------------------|--------|-------|----------------------------------|-------|

|       | (F)                                                | (V)                                                              | (H)                                         | (P3)   | (P2)  | (P1)                             | (P0)  |

| 1     | field bit<br>1st field: F = 0;<br>2nd field: F = 1 | vertical blanking bit<br>VBI: $V = 1$ ;<br>active video: $V = 0$ | H = 0 in SAV format;<br>H = 1 in EAV format | recomm | ,     | ation not<br>protectio<br>J 656) |       |

SAA4979H

## Sample rate converter with embedded high quality dynamic noise reduction and expansion port

#### 7.1.2 DOUBLE WINDOW AND PICTURE-IN-PICTURE PROCESSING

Data from the sub channel can be inserted into the data stream of the main channel by means of a fast switch. The two channels can be used together with one or two external field memories to implement, for example, double window or PIP processing. Both field based and frame based PIP processing is supported. The synchronization of the sub channel to the main channel is achieved by providing synchronized read signals (RE2 and RSTR2) for the external field memories, whereas the write signals need to be provided together with the incoming data by the external signal source.

A multi-PIP mode is also supported by freezing the data in the internal field memory within certain areas via the programmable internal control signal  $IE_{int}$ .

#### 7.1.3 BLACK BAR DETECTOR

Black bar detection searches for the last black line in the upper part of the screen and for the first black line in the lower part of the screen. The detection is done within a programmable window (control inputs: bbd\_hstart, bbd\_hstop, bbd\_vstart and bbd\_vstop). To avoid disturbances of LOGOs in the video, the window can be shifted to the horizontal centre of the lines. A video line is considered to be black if the luminance values of that line within the detection window are not greater than a certain slice level (control input: bbd\_slice\_level) for more than a specific number of pixels (control input: bbd\_event\_value).

The numbers of the first and the last active video line can be read out by the microcontroller (control outputs: bbd\_1st\_videoline and bbd\_last\_videoline).

### SAA4979H

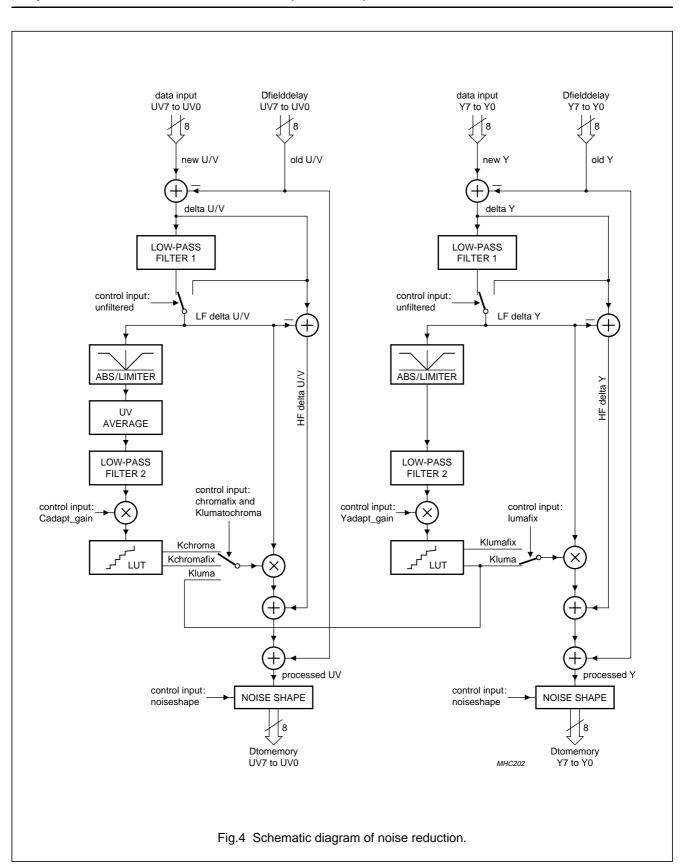

#### 7.1.4 DYNAMIC NOISE REDUCTION

The main function of the noise reduction is shown in Fig.4. It is divided into two signal paths for chrominance and luminance. In principal two operating modes can be used, the fixed and the adaptive mode. In both modes the applied frequency range, in which the noise reduction takes place, can be reduced or not reduced (control input: unfiltered).

The noise reduction operates field recursive with an averaging ratio (K factor) between fresh (new) and over previous fields averaged (old) luminance and chrominance values. Noise reduction can be activated by forcing the NREN control bit to HIGH. If NREN is LOW the noise reduction block is bridged via a data multiplexer.

In the fixed mode, the noise reduction produces a constant weighted input averaging. Because of smearing effects this mode should not be used for normal operation except for K = 1. The fixed mode can be activated separately for chrominance (control input: chromafix) and luminance (control input: lumafix).

In the adaptive mode, the averaging ratio is based on the absolute differences of the inputs of luminance and chrominance respectively. If the absolute difference is low, only a small part of the fresh data will be added. In cases of high difference, much of the fresh data will be taken. This occurs either in situations of movement or where a significant vertical contrast is seen. The relationship between the amount of movement and the K factor values is defined in a look-up table where the steps can be programmed (control input: Kstep). It should be noted that recursion is done over fields, and that pixel positions between the new and old fields always have a vertical offset of one line. So averaging is not only done in the dimension of time but also in the vertical direction. Therefore averaging vertically on, for example, a vertical black to white edge would produce a grey result.

The averaging in chrominance can optionally be slaved to the luminance averaging (control input: Klumatochroma), in that case chrominance differences are not taken into account for the K factor setting of the chrominance signal path.

The noise reduction scheme also decreases the cross-colour patterns effectively if the adaptive noise reduction for the averaging in chrominance is slaved to the luminance averaging (control input: Klumatochroma). The cross-colour pattern does not produce an increase of the measured luminance difference, therefore this pattern will be averaged over many fields.

#### 7.1.4.1 Band-splitting

The frequencies of the difference signals of luminance (delta Y) and chrominance (delta U/V) can be split optionally into an upper band (HF) and a lower band (LF) with a low-pass filter in both signal paths. The lower frequency band signals (LF delta Y and LF delta U/V) are used as input for the noise reduction function.

The lower frequency band of the difference signals can also be used for the motion detection. If, for example, only the lower frequency band contains information, the specific picture content does not move or is moving slowly.

Optionally it is possible to bridge the band-splitting (control input: unfiltered = 1).

#### 7.1.4.2 Motion detection

The same signals (the noise reduction is applied to) are also used to detect the amount of motion in the difference signals. Therefore, the absolute values of the difference signals are generated and limited to a maximum value. The absolute values of the difference signal of U and V are then averaged. The signals are low-pass filtered for smoothing these signals. The filtered signals are amplified, depending on the setting of the control inputs: Yadapt\_gain and Cadapt\_gain respectively.

The amplified signals, which correlate to the amount of movement in the chrominance or luminance signal path, are transferred into 1 out of 9 possible K factor values via look-up tables. The look-up tables consist of 9 intervals, each related to one K factor. The boundaries between the 9 intervals are defined by 8 programmable steps (control inputs: Kstep0 to Kstep7). The step values are valid for the look-up tables for both the chrominance and the luminance path. For example, signal values between Kstep2 and Kstep3 result in a K factor of K =  $\frac{3}{8}$ .

#### 7.1.4.3 K factor

The amount of noise reduction (field averaging) is described my means of the K factor. When K = 1 no averaging is applied and the new field information is used. When K = 0 no averaging is applied and thus only the old field information is used like in a still picture mode. All values inbetween mean that a weighted averaging is applied. It is possible to use fixed K factor values if the control inputs lumafix or chromafix are set to logic 1. The possible fixed K factor values of the control inputs Klumafix and Kchromafix are given in Table 6.

#### 7.1.4.4 Noise shape

Possible shadow picture information in the chrominance and luminance path, resulting from a low K factor value, will be eliminated if the noise shaping is activated. The noise shaping function can be switched off via the microcontroller (control input: noiseshape).

#### 7.1.5 NOISE ESTIMATOR

The noise level of the luminance signal can be measured within a programmable window (control inputs: ne\_hstart, ne\_hstop, ne\_vstart and ne\_vstop). The correlation in flat areas is used to estimate the noise in the video signal. A large number of estimates of the noise is calculated for every video field. Such an estimate is obtained by summing absolute differences between current pixel values and delayed pixel values within blocks of 4 pixels. Within the lower part of the total range of possible estimates 15 intervals are defined. Each interval is defined by a lower boundary and an upper boundary. The lower boundary is equal to the number of the interval, whereas the upper boundary has a fixed relationship to the lower boundary (control input: gain\_upbnd).

The lower boundary is increased or decreased by 1 in each field until an interval is found which contains at least a predefined number of estimates, and is at the same time lowest in the range. The value of the lower boundary of this interval determines the current noise figure output. The predefined number of estimates can be set via the microcontroller (control input: wanted\_value), and good results were obtained with a value which is approximately 0.27% of the total number of blocks.

For video fields with a lot of noise the number of small differences is very low, that means the number of noise estimates in the lower intervals is close to 0. Contrary to this, for clean sequences this number is very high. This means that for clean sequences the noise estimate figure will be close to 0, and for sequences with a lot of noise the noise estimate figure (control output: nest) will reach 15.

To improve the performance of the noise estimator, several functions are implemented which can be controlled by the microcontroller. To increase the sensitivity of the noise measurement a prefilter with different gain settings is available (control input: Ypscale). Since the video content, e.g. sequences with a lot of high frequencies, can influence the noise estimate figure, a detail-counter is built-in.

SAA4979H

The detail-counter calculates the number of absolute differences between current and previous pixels within a programmable interval defined by the control inputs lb\_detail and upb\_detail. The result of the 16-bit detail-counter (control outputs: detail\_cnt\_h and detail\_cnt\_l) can be used to increase or decrease the result of the noise estimation figure (control input: compensate).

In order to reduce the effect of clipping, only the blocks where the sum of the luminance value is within a predefined range are taken into account. The control signal clip\_offs can be used to increase or decrease this range. A grey-counter gives information whether enough pixels with values in the grey range are present in a video field (control output: grey\_cnt). When this number is lower than a predefined threshold, e.g. for complete fields towards black or white, all blocks are taken into account.

#### 7.2 Embedded DRAM

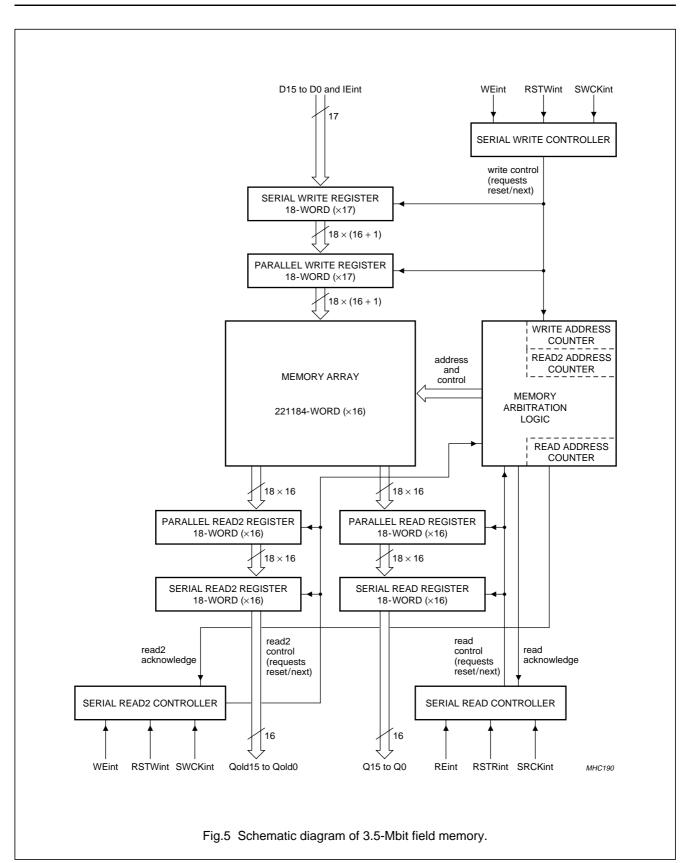

#### 7.2.1 3.5-MBIT FIELD MEMORY

The basic functionality of the field memory, which is shown in Fig.5, is similar to the SAA4956TJ. The memory size is extended to 3538944 bits. The data path is 16-bit wide (8-bit chrominance and 8-bit luminance). The field memory is capable of storing, for example, up to 307 video lines of 720 pixels in a 4 : 2 : 2 format. After writing or reading 18 words of 16-bit width, a data transfer is performed from the serial to parallel data registers (writing) or from the parallel to the serial registers (reading). The field memory has one write interface (controller and registers) to store 1f<sub>H</sub> data and two read interfaces, one to read field delayed 1f<sub>H</sub> data for the noise reduction function and the other to read 2f<sub>H</sub> data for the following data processing. Since two asynchronous clock domains are involved (SWCKint as 1f<sub>H</sub> clock and SRCKint as 2f<sub>H</sub> clock) the read and write access to the memory array is controlled asynchronously by the memory arbitration logic triggered via request and acknowledge pulses.

The write operation starts with a reset write (RSTWint) address pointer operation during the write enable (WEint) LOW phase. The RSTWint LOW-to-HIGH transition, referred to the rising edge of the write clock SWCKint, must be at least 18 clock cycles ahead of the first written data (WEint HIGH) and 18 clock cycles after the last written data. The reset write transfers data temporarily stored in the serial write registers to the memory array and resets the write counter to the lowest address. Write enable (WEint) is used to enable or disable a data write operation. The WEint signal controls the data inputs D0 to D15.

In addition, the internal write address pointer is incremented if WEint is HIGH at the positive transition of the SWCKint write clock. The data is latched if WEint was HIGH at the previous positive transition of SWCKint. Input enable (IEint) LOW can also suppress the storage of the data into the memory array but does not influence the write pointer increment. It is used to freeze parts of the field data e.g for PIP processing.

The read operation starts with a reset (RSTRint) of the read address pointer during the read enable (REint) LOW phase. The RSTRint LOW-to-HIGH transition, referred to the rising edge of the read clock SRCKint, must be at least 18 clock cycles ahead of the first read data (REint HIGH) and 18 clock cycles after the last read data. The reset read resets the read counter to the lowest address and requests a read operation of the data of the lowest address to the serial read register. Read enable (REint) is used to enable or disable the read operation. The REint controls the data outputs Q0 to Q15. REint HIGH increments the read counter.

In parallel to the write operation a read2 operation is done using the same control signals as the write operation: SWCKint, WEint and RSTWint. It reads the old data of the previous field. The data Qold is needed as data input (Dfielddelay) for the noise reduction.

When the WEint signal is HIGH it indicates that active video (valid  $1f_H$  data) is to be stored. The start of WEint HIGH is triggered by the H and V status bits of the ITU data stream. The start of WEint HIGH can be delayed by the control signals weint\_hstart (number of clock delays) and weint\_vstart (number of video lines delay). The stop of WEint HIGH is controlled by weint\_hstop and weint\_vstop.

When the IEint signal is HIGH it indicates that active video (valid  $1f_H$  data) is also to be stored. The video data is not stored and earlier written data is maintained (frozen) if WEint is HIGH and IEint is LOW. The start of IEint HIGH is triggered by the H and V status bits of the ITU data stream. The start of IEint HIGH can be delayed by the control signals ieint\_hstart (number of clock delays) and ieint\_vstart (number of video lines delay). The stop of IEint HIGH is thigh is controlled by ieint\_hstop and ieint\_vstop.

RSTWint is triggered by the V status bit of the ITU data stream.

RSTRint is identical to the VD output signal.

REint is provided by the following sample rate conversion to gather  $2f_H$  data if it is needed.

### SAA4979H

#### 7.3 Digital processing at 2f<sub>H</sub> level

#### 7.3.1 SAMPLE RATE CONVERSION

The sample rate conversion block is used to obtain 848 active pixels per line out of the original 720 pixels according to the relation of the two sampling frequencies (32 MHz and 27 MHz). The interpolation for phase positions between the original samples is achieved with a variable phase delay filter with 10 taps for luminance signals and 6 taps for chrominance signals.

The conversion to a higher sample frequency of 32 MHz is done to improve the motion estimation performance in combination with external feature ICs, which can process up to 848 pixels per line at a 32 MHz clock. Bypassing this function keeps the original 720 pixels per line (control input: bypass\_FSRC).

#### 7.3.2 EXPANSION PORT

For a further extension of the system an expansion port is available, which is applicable for either a 4:2:2 format or a reduced 4:1:1 format for data input and output at a 32 MHz line-locked clock; see Table 3. However, the internal data is processed in a 8-bit wide 4:2:2 format.

To generate the 4 : 1 : 1 format at the output the U and V samples from the 4 : 2 : 2 data stream are filtered by a low-pass filter, before being subsampled with a factor of 2 and formatted to 4 : 1 : 1 format. Bypassing this function keeps the data in the 4 : 2 : 2 format.

An internal bandwidth detector is implemented to detect whether the colour difference signals provide either the full 4:2:2 bandwidth or a reduced 4:1:1 bandwidth. Therefore absolute differences between original data and downsampled data are calculated and can be read out by the microcontroller (control output: UV\_bw\_detect). Low absolute differences indicate that the original data does not contain the full 4:2:2 bandwidth. This information can be used to switch the upsample and downsample filter on or off (control inputs: bypass\_upsampling and bypass\_downsampling). Bandwidth detection is done within a programmable window (control inputs: bw\_hstart, bw\_hstop and bw\_vstart, bw\_vstop).

In the event of a 4:1:1 format at the input an upconverter to 4:2:2 is applied with a linear interpolation filter for creation of the extra samples. These are combined with the original samples from the 4:1:1 stream.

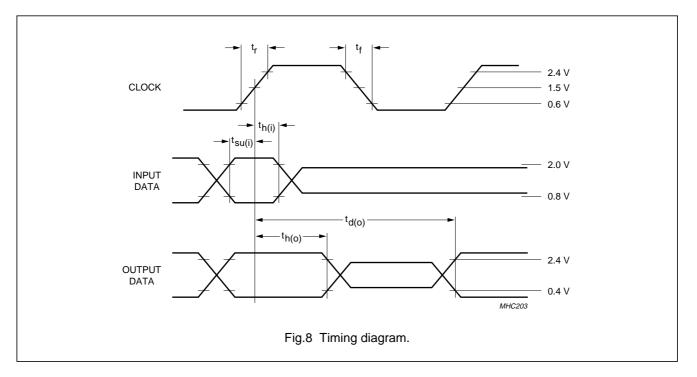

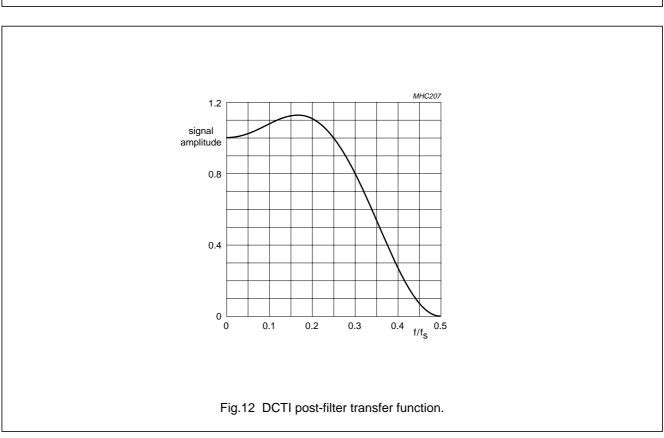

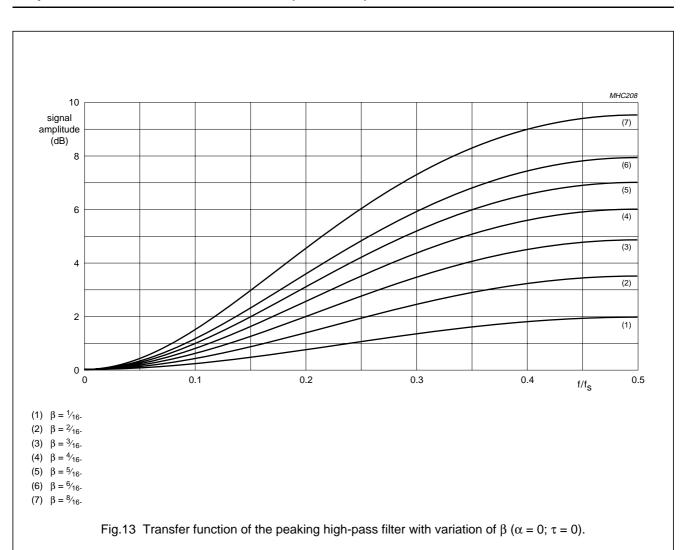

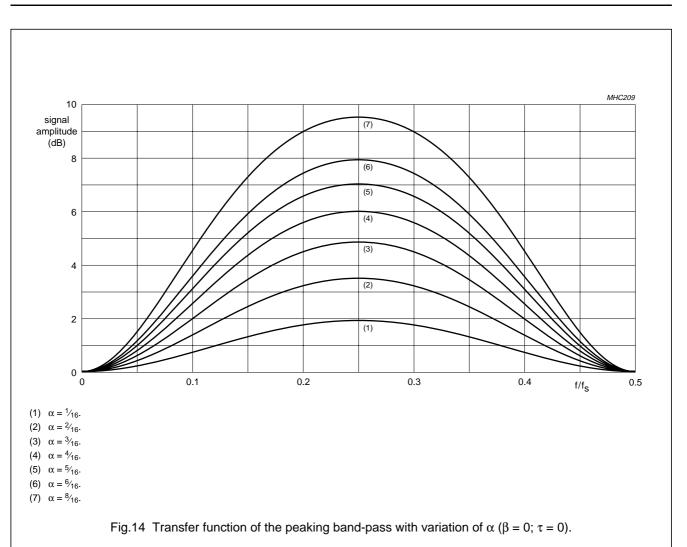

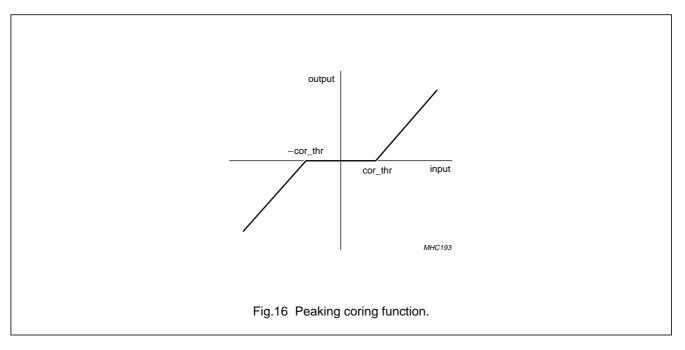

The first phase of the YUV data stream is available on the output bus two clock cycles after the rising edge of the REI input signal. The start position, when the first phase of the YUV data stream arrives on the input bus, can be set via the control register exp\_hstart.